Cross-Layer Solutions Enabling Instant Computing for Edge Intelligence Devices Image

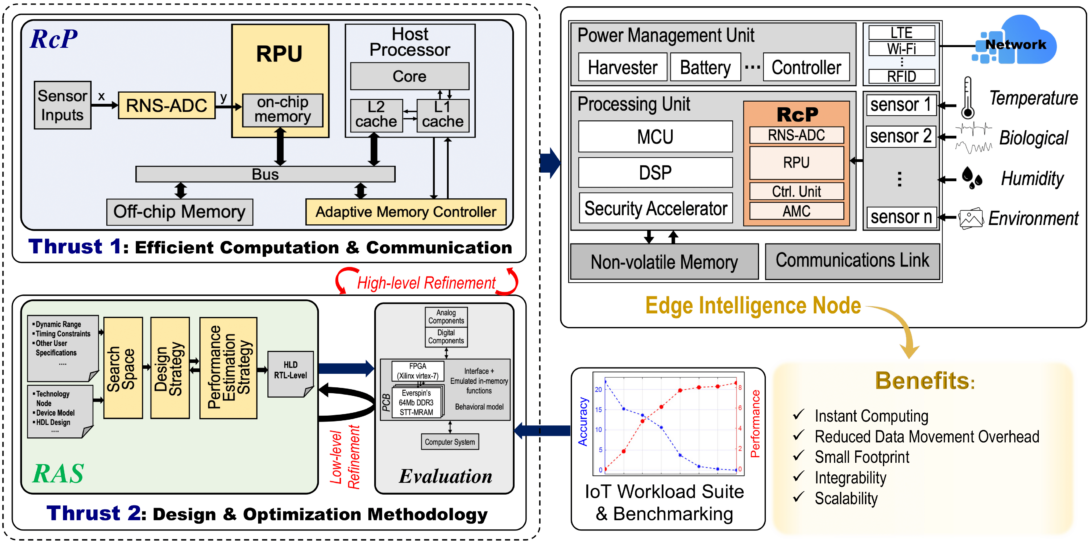

This project addresses these challenges by developing computing architectures that are high-speed, energy-efficient, and normally off under regular conditions. The research focuses on integrating sensing computation for resource-limited sensory nodes, combining cross-layer post-CMOS methodologies with non-volatile devices. By leveraging always-on sensing and normally-off computing and ensuring intermittent-robust computation through secure storage of intermediate circuit values, this work aims to revolutionize IoT device operations, making them more resilient, energy-efficient, and capable of handling power outages.

Cross-Layer Solutions Enabling Instant Computing for Edge Intelligence Devices Image

This project focuses on developing low-cost, efficient design strategies for real-time processing and decision-making systems across multiple design abstraction levels. Key objectives include:

- Designing low-power, area-efficient integrated converters, such as Binary-to-Residue Number Systems (RNS) and Analog-to-Digital Converters (ADC).

- Proposing a reconfigurable near-sensor RNS processing unit (RPU) to accelerate low-bit-width neural networks, enabling intelligent IoT devices. The RPU can perform MAC operations with one-cycle latency while maintaining memory function and capacity, handling essential layers like activation and normalization.

- Creating an automated exploration tool called Residual Architecture Search (RAS) to optimize processing units’ architecture for various applications, improving metrics like energy efficiency and performance.

- Developing a cross-layer evaluation framework, including FPGA-magnetic RAM prototypes, and testing architectures with RISC-V processors on real-world IoT applications.

Supported By NSF

Collaborator: NJIT